# In As Nanowire with Epitaxial Aluminum as a Single-Electron Transistor with Fixed Tunnel Barriers

M. Taupin, <sup>1,\*</sup> E. Mannila, <sup>1</sup> P. Krogstrup, <sup>2</sup> V. F. Maisi, <sup>1,2</sup> H. Nguyen, <sup>1,2,3</sup> S. M. Albrecht, <sup>2</sup> J. Nygård, <sup>2</sup> C. M. Marcus, <sup>2</sup> and J. P. Pekola <sup>1</sup>

<sup>3</sup>Nano and Energy Center, Hanoi University of Science, VNU, 120401 Hanoi, Vietnam (Received 15 April 2016; revised manuscript received 17 October 2016; published 28 November 2016)

We report on the fabrication of single-electron transistors using InAs nanowires with epitaxial aluminum with fixed tunnel barriers made of aluminum oxide. The devices exhibit a hard superconducting gap induced by the proximized aluminum cover shell, and they behave as metallic single-electron transistors. In contrast to the typical few-channel contacts in semiconducting devices, our approach forms opaque multichannel contacts to a semiconducting wire and, thus, provides a complementary way to study them. In addition, we confirm that unwanted extra quantum dots can appear at the surface of the nanowire. Their presence is prevented in our devices and also by inserting a protective layer of GaAs between the InAs and Al, the latter being suitable for standard measurement methods.

#### DOI: 10.1103/PhysRevApplied.6.054017

## I. INTRODUCTION

Semiconducting nanowires (NWs) are widely used nowadays in nanotechnology [1-3], as their transport properties can be easily tuned [4,5]. In particular, InAs NWs are of interest as they are optically active [6] and can act as a field-effect transistor [7], a quantum dot [8-13], or a qubit [14]. Recently, the growth of a NW with a highquality interface between InAs and aluminum has been achieved [15], with a hard superconducting gap [16], systems in which Majorana bound states have been observed [17-20]. In these devices, the barriers are formed electrostatically to allow great flexibility of the barrier strength, contrary to "fixed" tunnel barriers one can find in metallic single-electron transistors (SETs). However, the drawback of this flexibility is the limited number of open conductive channels [20,21] which can either limit the signal in case of large opacity of the barriers or induce a leakage current in the other limit.

In this paper, we present a simple device in an InAs NW proximized with epitaxial Al. The main idea is to use the aluminum shell on top of the InAs NW to form a fixed tunnel barrier, thus, with InAs as a SET, as in a metallic system [22,23]. Compared to electrostatic tunnel barriers, aluminum-oxide-based tunnel contacts are known to possess superior properties: They have a large number of conduction channels, typically of the order of 10<sup>4</sup> [24,25].

It allows one to make them several orders of magnitude more opaque than the few-channel contacts without losing signal strength. The more opaque the tunnel junctions are, the better the approximation of sequential tunneling is. Hence, when probing the hardness of the superconducting gap, we observe consistently an order of magnitude lower leakage levels in the gap. For this reason, the combination of a metallic SET and a proximized InAs NW can give access to functionalities mixing SET and InAs NWs properties not possible with standard techniques. In addition, our method reduces some technical difficulties: Only one gate per intentional quantum dot (QD) is needed, and it ensures good contacts between the NW and the external leads. It also prevents the appearance of parasitic effects due to the exposure of the InAs core during the fabrication process, as the InAs core as well as the interface between InAs and Al remain intact. Such effects are prevented as well by inserting a protective layer between the In As core and the Al layer. Several works already exist on the fabrication of a SET using semiconducting NWs with fixed tunnel barriers (i.e., not tunable by gate modulation) with, e.g., Si NWs [26,27] or InAs/InP heterostructures [28].

## II. FABRICATION

The hexagonal InAs NWs are grown by molecular beam epitaxy (MBE) using gold nanoparticle catalysts and are 10– $15~\mu m$  long. The aluminum is then deposited epitaxially, covering entirely the NW, without breaking the vacuum to guarantee a good interface between InAs and Al [15]. For some NWs, a buffer layer of GaAs, 5 nm thick, is grown on top of the InAs, followed then by the Al deposition. These NWs form a stacking-fault-free wurtzite

<sup>&</sup>lt;sup>1</sup>Low Temperature Laboratory, Department of Applied Physics, Aalto University School of Science, P.O. Box 13500, FI-00076 Aalto, Finland

<sup>&</sup>lt;sup>2</sup>Center For Quantum Devices, Niels Bohr Institute, University of Copenhagen, Universitetsparken 5, 2100 Copenhagen Ø, Denmark

Present address: Institute of Solid State Physics, TU Wien, Wiedner Hauptstrasse 8-10, 1040 Vienna, Austria. mathieu.taupin@ifp.tuwien.ac.at

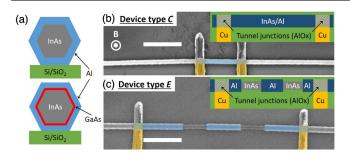

FIG. 1. (a) Sketch of the cross section of the NW. The aluminum shell (symbolized in blue) is grown epitaxially either directly on the InAs wire, in gray (upper sketch, devices named "-Al") or on an intermediate protective GaAs shell (lower one, named "-GaAs"). (b),(c) Sketch and SEM image of a device type C, with a fully covered wire, and of a device type E, with an isolated aluminum island. The leads and the side gate (not shown) are made of copper (in orange), with a thickness from 100 to 200 nm, and the tunnel barriers are formed of aluminum oxide and are situated on the hatched surfaces. The not-drawn areas on the devices are supposed to play no role in the properties of the system. The white bars represent 1  $\mu$ m.

phase, with misfit dislocations at the InAs/GaAs interface due to the 7% lattice mismatch; therefore, the strain relaxes very quickly [29]. This intermediate GaAs layer is expected to reduce the stress at the surface of the InAs and improve the intrinsic properties of the NW (like, e.g., carrier mobility), as already observed in various NWs with cover shells [30–34]. A sketch of the cross section of the wires is shown Fig. 1(a). The devices with the GaAs-covered shell are named "-GaAs" and the others, with only the aluminum shell, are named "-Al." We remind that the NWs with the GaAs layer also have an epitaxial layer of Al. We have a clean contact between the core and the Al layer which leads to a negligible energy barrier (i.e., no tunnel barrier is formed between the NW core and the superconducting layer) as shown previously [15,16].

The NWs are transferred from the growth chip on a premarked substrate by dry deposition. The substrate is a highly doped silicon wafer covered by 200 nm of silicon oxide and is used as a backgate. The position of the NWs is found on the chip using a scanning electron microscope

(SEM). In order to study the effect of the chemical etching, we first isolate an Al island (approximately 1  $\mu$ m long) in the middle of the NW, by etching chemically at two places a 0.5- to 1-um segment of the Al shell by immersion in MF-CD-26 for 90 s at room temperature (called device E, for "etched"). The remaining Al on the central island and on each side of the wire close to the junctions is supposed to keep the proximized superconductivity intact and uniform over the entire NW. The other type of device is made without the chemical etching, keeping the aluminum shell intact and, thus, without any bare InAs (called device C, for "covered"). The premarked chip is then covered with a resist, and the two leads and the side gate are patterned by electronbeam lithography. After development, the premarked chip is inserted in an electron-beam evaporator equipped with a plasma gun. The native oxide layer on Al is removed by argon plasma etching inside the evaporator chamber. The epitaxial Al is then reoxidized under O<sub>2</sub> atmosphere of 2 mbar for 2 min to create the tunnel barriers, approximately 0.5 to 1 nm thick [35]. Next, 150 to 200 nm of Cu is evaporated in order to make the leads and the side gate. The fact that the native Al oxide is etched in situ ensures good control of the tunnel junctions. The tunnel barriers are expected only at the junctions, and no barrier should form inside the NW. The junctions cover 150 to 300 nm over the wire depending on the device and are spaced by 1  $\mu$ m (for the device C-Al') and 5  $\mu$ m for the others. During the plasma etching and the oxygen reoxidation, the InAs core is protected either by the Al shell where the junctions are made and by the resist everywhere else. Therefore, we do not expect these treatments to damage further the InAs core. We emphasize that only Cu is deposited on the premarked chip; i.e., no Al layer is added: The tunnel junctions are formed by reoxidizing the epitaxial Al layer grown from the MBE process after etching the native oxide layer. The sketches and SEM images of the devices are shown Figs. 1(b) and 1(c). The main parameters of the samples are given in Table I. The NWs from the devices E-Al and C-Al come from the same growth, and the same applies for the devices E-GaAs and C-GaAs. The smaller resistance and charging energy of the device E-GaAs come from its wider tunnel junctions compared to the other devices. Only the backgate is used

TABLE I. Summary of the main parameters of devices obtained by fitting the normal state at  $T_{\text{bath}}$ : the total resistance across the whole device at low temperature  $R_T$ , the superconducting gap  $\Delta$ , the charging energy  $E_c$ , the diameter of the InAs core  $\phi_{\text{InAs}}$ , the thickness of the aluminum layer  $t_{\text{Al}}$ , and of the GaAs layer  $t_{\text{GaAs}}$ . The device C-Al' is similar to the device C-Al with a different size.

| Name   | $R_T$                            | Δ (μeV)          | $E_c \; (\mu {\rm eV})$ | $\phi_{\mathrm{InAs}}$ (nm) | t <sub>Al</sub> (nm) | t <sub>GaAs</sub> (nm) |

|--------|----------------------------------|------------------|-------------------------|-----------------------------|----------------------|------------------------|

| E-Al   | $180 \text{ k}\Omega^{\text{a}}$ | 130 <sup>a</sup> | 40 <sup>a</sup>         | 70                          | 20                   | Not applicable         |

| C-Al   | $22 \text{ k}\Omega$             | 202              | 45                      | 70                          | 20                   |                        |

| C-Al'  | $126 \text{ k}\Omega$            | 192              | 30                      | 40                          | 20                   | Not applicable         |

| E-GaAs | 64 kΩ                            | 195              | 10                      | 50                          | 25                   | 5                      |

| C-GaAs | 19 MΩ                            | 195              | 65                      | 50                          | 25                   | 5                      |

$<sup>^{\</sup>mathrm{a}}$ Taken at  $V_{\mathrm{BG}}=2$  V.

in this study, but we obtain similar results using the side gate. All the measurements presented here are performed in a dilution fridge at a bath temperature  $T_{\rm bath} \simeq 60$  mK and, when applied, the magnetic field is perpendicular to the NW [see Fig. 1(b)]. In the last section, conductance measurements are performed, a lock-in amplifier is used with the excitation voltage ranging from  $V_{\rm ac}=2$  to  $10~\mu{\rm V}$ , and the frequency from  $f\approx 0.7$  to 300 Hz depending on the gain and the bandwidth of the voltage and current amplifiers used.

According to Ref. [36], the capacitance of the NW on the highly doped Si substrate is estimated to be  $C_g \sim 0.25$  fF for each device. We can then estimate the capacitance of the junctions supposing they cover half a cylindrical NW (we cannot evaporate below the NW). In the case of aluminum oxide, we use the dielectric constant  $\epsilon_r \approx 4$  and the oxide thickness between 0.5 and 1 nm [35]. Thus, we obtain the capacitance per junction  $C_J \sim 1$  fF and, therefore, the total capacitance  $C_\Sigma = C_g + 2C_J \sim 2.25$  fF, which gives the charging energy  $E_C = e^2/(2C_\Sigma) \sim 35~\mu\text{eV}$ , close to the experiment. The total capacitance of the devices is mainly caused by the junctions, which are rather wide in our devices.

### III. CHARACTERIZATION OF THE DEVICES

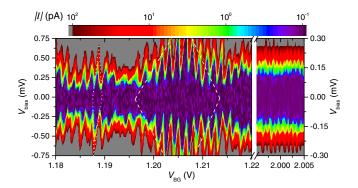

We first study the device E-Al, Fig. 1(c), in which the InAs core is exposed. Here, we choose the wire without GaAs and etch Al in selected areas. The effect of the backgate on electron-transport measurements is shown in Fig. 2. At negative backgate values  $V_{\rm BG} < 0$  (not shown), the transport is blocked. For  $0 < V_{\rm BG} < 2$  V, a complex stability diagram is present, with at least two sets of Coulomb diamonds (see, e.g., the white dotted and dashed diamonds in the left-hand side of Fig. 2). Only one QD is expected with a small charging energy. However, the QDs measured at intermediate gate values around 1.2 V show a charging energy between 0.3 and 0.8 meV, too high to

FIG. 2. Current I vs bias  $V_{\rm bias}$  and backgate  $V_{\rm BG}$  of the device E-Al centred at 1.2 and 2 V, respectively. Several sets of Coulomb diamonds are visible, with different gate periodicity and amplitude; see, e.g., the white dashed and white dotted diamonds. Note the different vertical scales between the left and right part of the graphs.

reflect the main dot. These large values as well as the aperiodicity of the diamonds with  $V_{\rm BG}$  are signatures of the presence of several QDs. Similar behavior is observed in several of our devices of the same type, and unwanted QDs have as well been reported in previous studies, despite the high quality of the NWs used [16,37,38]. It is believed to be caused by defects [39] and potential fluctuations at the surface of the NW [40] which can be triggered by chemical and/or plasma treatments of the NW. One reason for their presence comes from the fabrication process: The contacts on the NW are made directly on it, and in order to have an Ohmic contact or to etch away a surface layer (the Al epitaxial layer in our case; see, e.g. the devices in Refs. [20,21]), additional chemical or plasma cleaning of the surface may be needed. These processes may deteriorate the surface of InAs, thus, increasing the likelihood of forming unwanted QDs whose locations and sizes are not controlled. It is, nevertheless, possible to make them transparent by tuning locally its potential with additional side gates, leading to the fabrication of complex devices with potentially unnecessary side gates (see, e.g., some of the devices in Ref. [20]). The transparency of the unwanted QDs is achieved in our situation by increasing the backgate voltage: Above  $V_{\rm BG} \sim 2~{\rm V}$ , although deformed, the stability diagram is more regular and periodic with  $V_{\rm BG}$ (right-hand side of Fig. 2), similar to a metallic device. This stability diagram represents the intended dot with a charging energy of approximately 40 µeV. The superconducting gap is, however, small in this device compared to the other ones (see Table I). One possible reason for this is that the extra QDs affect the superconducting state of the NW.

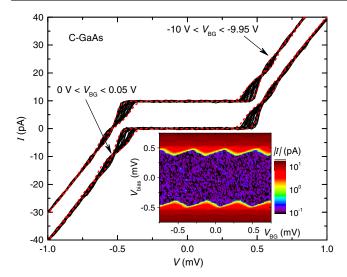

In our other devices, the InAs core is unexposed and always covered by another layer, either by the Al shell (device C-Al), by a protective GaAs shell (device E-GaAs), or by both (device C-GaAs). In the linear Ohmic regime, at large bias voltage values, these devices exhibit a metallic behavior: The transport is independent of the backgate value (no noticeable differences are seen for  $V_{BG}$  in the range -5 to 5 V). The I-V characteristics of the device C-GaAs at the backgate positions close to -10 and 0 V are shown in Fig. 3. Both sets of *I-V* characteristics are similar, confirming the metalliclike state of our device. The dashed lines correspond to a theoretical fit of the normal state used for a metallic SET with a superconducting island [23]: The agreement between the measurements and the fit is very good. The parameters used for the fit are given in Table I and are the same for both measurements. The theoretical model also nicely fits the *I-V* characteristics of the other devices (not shown) in the normal state. This indicates that the QD measured is different from the one measured in the device E-Al, as the properties of the devices (total resistance, charging energy, and superconducting gap) do not change with the gate voltage. The inset is the stability diagram around  $V_{BG} = 0 \text{ V}$ , exhibiting periodic and

FIG. 3. *I-V* characteristics of the device *C*-GaAs taken at several backgate positions close to -10 V (upper curve) and 0 V (lower curve). The upper curve is shifted by 10 pA for visibility. The dashed lines correspond to theoretical fits, with the same parameters for both measurements. The inset is the stability diagram centred at  $V_{\rm BG}=0$  V.

regular Coulomb diamonds. The metallic behavior (i.e., the absence of gate dependence in the transport besides the Coulomb blockade regime) is evidence of the absence of undesirable QDs and that the transport is governed by only one intrinsic QD.

The comparison of the transport measurements at low bias voltage in the gate-open state of the three devices is

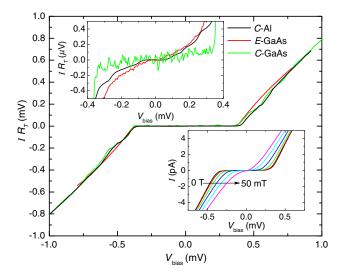

FIG. 4. I-V characteristics of the devices C-Al, E-GaAs, and C-GaAs. The vertical axis is the product of the current and the resistance of the device  $I \cdot R_T$  to normalize the measurements. The upper inset is a magnification in the subgap state and the lower one the field dependence of a device similar to C-Al, from B=0 to 50 mT with 10-mT steps. The measurements are done in the gate-open state.

shown in Fig. 4. To present all the samples on the same footing, we plot the product of the current and the resistance  $I \cdot R_T$ . The three devices are similar with the main difference being the charging energy. The upper inset shows the magnification of the measurements in the superconducting state. All devices have a superconducting gap similar to that of Al, approximately 200  $\mu$ eV. The slope of the *I-V* characteristics in the superconducting state is a signature of the hardness of the gap, and the ratio between the conductance in the superconducting state  $G_S$  and in the normal state  $G_N$  is  $G_S/G_N \lesssim 10^{-3}$ , a measure of the hard gap of our system. As we have opaque transport channels, we now obtain an order of magnitude lower ratios proving that the gap in the NWs is even an order of magnitude harder than estimated earlier in Ref. [16]. The hard gap is not affected by etching the Al shell in the device E-GaAs, since the value measured equals the gap at the proximity of the junctions, where the Al shell is not etched chemically. The lower inset shows the field dependence of a device similar to C-Al, from B = 0 to 50 mT, close to the critical field measured at  $B_{c2} \approx 55$  mT. The main effect of the magnetic field in the region  $|eV_{\text{bias}}| \ge 2\Delta(B)$  is to close the superconducting gap: From this point of view, our devices are identical to metallic SETs and do not seem to present any additional interest. Thus, we will not focus on the normal state under field any longer.

The devices we show can be used for future studies of the properties of proximized superconductivity as our method is relatively noninvasive. Until now, the SET regime in proximized InAs NWs was achieved only by tuning the potential of the wire with gates [20,21]. However, the transport properties of the system can be very sensitive to the gate positions, and corrections have to be applied in case of cross talk between the leads and the gates or between each gate. With one gate only, the cross talk is less problematic, and we, thus, have a possibility to perform more advanced experiments, such as using the devices as a turnstile [41]. The charging energy of our device can be easily increased by decreasing the dimensions of the NW (total length and diameter), the size of the QD (junctions spacing), or the size of the junctions.

The similarity between the devices *C*-Al and *C*-GaAs suggests that NWs with a GaAs cover shell can be used for a SET setup, and the similarity between the devices *C*-GaAs and *E*-GaAs demonstrates that the GaAs layer prevents the formation of extra QDs and that the properties of the devices are not caused only by the Al layer but also by the core. From the present results, it cannot yet be concluded if the GaAs cover shell improves the intrinsic properties of a NW (higher mobility of carriers or "harder" superconducting gap). When Al etching is necessary to use electrostatic barriers, for example, the GaAs cover shell may be used to prevent the appearance of unwanted QDs without affecting the proximity effect. The cover shell will give the opportunity to focus in the future on the intrinsic

properties of the wires using devices with electrostatic barriers or with NWs half covered with Al. Although it is possible to form Ohmic contacts directly on InAs, this extra protective shell should also be compatible with good contacts to the external leads made afterwards.

### IV. IN-GAP MEASUREMENTS

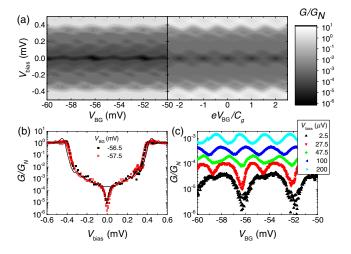

We now present a study of a device similar to the device C-Al presented above, called C-Al'. The parameters of this device are listed in Table I: the NW is smaller and the junctions are 1  $\mu$ m from each other. The Al layer of both extremities of the NW (beyond the junctions) is chemically etched. Note that in this paragraph, conductance (and not resistance) measurements are shown. The device displays regular Coulomb diamonds with a stability diagram similar to the one given in the inset of Fig. 3. Therefore, we focus in the subgap regime with  $|eV_{\text{bias}}| \leq 2(\Delta + E_c)$ . Figure 5 shows the conductance measurements at zero field with the theoretical model (see below). In Fig. 5(a), the experimental (on the left-hand side) and modeled (right-hand side) stability diagram show clear Coulomb features in the subgap regime, and Figs. 5(b) and 5(c) are the measurements at constant  $V_{\rm BG}$  and  $V_{\rm bias}$ , respectively. The difference between the gate-open to the gate-close state is more visible in Fig. 5(b), and a clear dip close to  $V_{\text{bias}} = 0$  is present. Close to  $V_{\rm bias}=0$ , the ratio of the conductances reaches  $G_S/G_N \sim 10^{-6}$  and  $G_S/G_N \sim 10^{-3}-10^{-4}$  at low bias outside the dip, highlighting the good quality of the proximized superconductivity. Figure 5(c) shows the Coulomb oscillations with the gate and their period doubling when  $|V_{\rm bias}| \le 50 \ \mu \rm V$ , i.e., when the bias voltage is

FIG. 5. Conductance measurement of the device C-Al'. (a) Experimental (on the left) and theoretical (in the right) stability diagram with clear Coulomb features in the subgap regime. (b) Measurements at constant backgate voltage with the theoretical fits in solid lines. (c) Coulomb oscillation of the conductance with the backgate at constant bias; a change of periodicity is occurring at  $V_{\rm bias} \approx 50~\mu{\rm V}$ .

smaller than the charging energy. These features—change of periodicity from 1e to 2e of the Coulomb oscillations and pronounced dip at low bias—are robust and are observed in several devices. A similar pronounced minimum in the conductance as the one we observe has already been reported in proximized NWs [42] and is attributed to the Coulomb blockade regime but with a conductance ratio  $G_S/G_N$  several orders of magnitude larger than in our device.

The model of the conductance measurements shown Fig. 5 is similar to the simple one used in Fig. 3 taking into account the normalized Dynes density of states in the superconducting state [43,44]

$$n_D(E) = \left| \operatorname{Re} \frac{E/\Delta + i\gamma}{\sqrt{(E/\Delta + i\gamma)^2 - 1}} \right| \tag{1}$$

with  $\gamma$  the Dynes parameter. The model shown in Fig. 5 uses  $\gamma = 6 \times 10^{-4}$  and the parameters in Table I. It reproduces relatively well the measurements as shown Fig. 5, except for the low-bias-voltage regime. Indeed, in this range the theoretical fit cannot reproduce the 2e periodicity of the oscillations and tends to overestimate the conductance. The origin of the 2e periodic signal and of the dip at low bias voltage is not clear yet, but they might come from localized in-gap states, which have been observed in similar devices using the same type of NW [21]. A more advanced model is, therefore, needed to describe fully our system, and devices with higher charging energy will be useful in order to disentangle accurately the effect of these potential in-gap states to the Coulomb blockade regime.

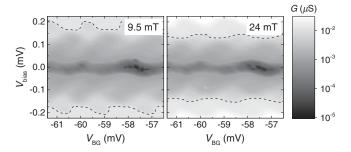

Figure 6 shows the stability diagram at low bias of the device C-Al' at B = 9.5 mT (left-hand side) and B = 24 mT  $\approx B_{c2}/2$  (right-hand side). The main effect of the magnetic field is to reduce the superconducting gap, as shown by the isoconductance lines (dashed lines in Fig. 6 at 10 nS) going closer to zero bias, the in-gap features at low bias voltage being relatively field insensitive below 30 mT. By increasing further the magnetic field, the 2e periodic signal eventually vanishes, and the superconducting gap

FIG. 6. Stability diagram at low bias taken at 9.5 mT (on the left) and at 24 mT (on the right). The dashed lines are the isoconductance lines at G = 10 nS.

closes completely. The complete study of the magnetic field and temperature dependence of the subgap features are needed to get a better understanding.

### V. CONCLUSION

In conclusion, we demonstrate that InAs nanowires proximized with aluminum can be used as a single-electron transistor with a hard superconducting gap by forming a fixed tunnel barrier based on the aluminum shell. Our results confirm that unwanted quantum dots can appear on the surface of the InAs core when bare. As for our devices. the aluminum shell does not have to be etched, and this prevents the formation of these extra quantum dots. They can be avoided when an additional thin protective layer of GaAs is inserted between the InAs and the aluminum, without seemingly degrading the transport or the superconducting properties of the system. Our technique provides a way to minimize the number of gates needed for nanowire-based devices. This gives an opportunity to use an InAs nanowire as an island of a single-electron transistor with the rich properties of a nanowire.

### ACKNOWLEDGMENTS

We thank M. Meschke and J. T. Peltonen for technical advice and N. Paillet for help in plasma etching. This work is supported by Academy of Finland (Projects No. 272218 and No. 284594), by Danish National Research Foundation, and by Microsoft Project Station Q. We acknowledge the availability of the facilities and technical support by Otaniemi research infrastructure for Micro and Nanotechnologies (OtaNano).

- [1] L. Samuelson, C. Thelander, M. T. Björk, M. Borgström, K. Deppert, K. A. Dick, A. E. Hansen, T. Mårtensson, N. Panev, A. I. Persson, W. Seifert, N. Sköld, M. W. Larsson, and L. R. Wallenberg, Semiconductor nanowires for 0*d* and 1*d* physics and applications, Physica (Amsterdam) **25E**, 313 (2004).

- [2] C. Thelander, P. Agarwal, S. Brongersma, J. Eymery, L. F. Feiner, A. Forchel, M. Scheffler, W. Riess, B. J. Ohlsson, U. Gösele, and L. Samuelson, Nanowire-based one-dimensional electronics, Mater. Today 9, 28 (2006).

- [3] C. M. Lieber and Z. L. Wang, Functional nanowires, MRS Bull. 32, 99 (2007).

- [4] Y.-J. Doh, J. A. van Dam, A. L. Roest, E. P. A. M. Bakkers, L. P. Kouwenhoven, and S. De Franceschi, Tunable supercurrent through semiconductor nanowires, Science 309, 272 (2005).

- [5] D. Liang, J. Du, and X. P. A. Gao, InAs nanowire devices with strong gate tunability: Fundamental electron transport properties and application prospects: A review, J. Mater. Sci. Technol. 31, 542 (2015).

- [6] Y. Li, F. Qian, J. Xiang, and C. M. Lieber, Nanowire electronic and optoelectronic devices, Mater. Today 9, 18 (2006).

- [7] T. Bryllert, L.-E. Wernersson, L. E. Froberg, and L. Samuelson, Vertical high-mobility wrap-gated InAs nanowire transistor, IEEE Electron Device Lett. 27, 323 (2006).

- [8] M. T. Björk, C. Thelander, A. E. Hansen, L. E. Jensen, M. W. Larsson, L. R. Wallenberg, and L. Samuelson, Few-electron quantum dots in nanowires, Nano Lett. 4, 1621 (2004).

- [9] J. A. van Dam, Y. V. Nazarov, E. P. A. M. Bakkers, S. De Franceschi, and L. P. Kouwenhoven, Supercurrent reversal in quantum dots, Nature (London) 442, 667 (2006).

- [10] T. Sand-Jespersen, J. Paaske, B. M. Andersen, K. Grove-Rasmussen, H. I. Jørgensen, M. Aagesen, C. B. Sørensen, P. E. Lindelof, K. Flensberg, and J. Nygård, Kondo-Enhanced Andreev Tunneling in InAs Nanowire Quantum Dots, Phys. Rev. Lett. 99, 126603 (2007).

- [11] E. J. H. Lee, X. Jiang, R. Aguado, G. Katsaros, C. M. Lieber, and S. De Franceschi, Zero-Bias Anomaly in a Nanowire Quantum Dot Coupled to Superconductors, Phys. Rev. Lett. 109, 186802 (2012).

- [12] W. Chang, V. E. Manucharyan, T. S. Jespersen, J. Nygård, and C. M. Marcus, Tunneling Spectroscopy of Quasiparticle Bound States in a Spinful Josephson Function, Phys. Rev. Lett. 110, 217005 (2013).

- [13] E. J. H. Lee, X. Jiang, M. Houzet, R. Aguado, C. M. Lieber, and S. De Franceschi, Spin-resolved Andreev levels and parity crossings in hybrid superconductor-semiconductor nanostructures, Nat. Nanotechnol. 9, 79 (2014).

- [14] S. Nadj-Perge, S. M. Frolov, E. P. A. M. Bakkers, and L. P. Kouwenhoven, Spin-orbit qubit in a semiconductor nanowire, Nature (London) 468, 1084 (2010).

- [15] P. Krogstrup, N. L. B. Ziino, W. Chang, S. M. Albrecht, M. H. Madsen, E. Johnson, J. Nygård, C. M. Marcus, and T. S. Jespersen, Epitaxy of semiconductor-superconductor nanowires, Nat. Mater. 14, 400 (2015).

- [16] W. Chang, S. M. Albrecht, T. S. Jespersen, F. Kuemmeth, P. Krogstrup, J. Nygård, and C. M. Marcus, Hard gap in epitaxial semiconductor-superconductor nanowires, Nat. Nanotechnol. 10, 232 (2015).

- [17] R. M. Lutchyn, J. D. Sau, and S. Das Sarma, Majorana Fermions and a Topological Phase Transition in Semiconductor-Superconductor Heterostructures, Phys. Rev. Lett. **105**, 077001 (2010).

- [18] Y. Oreg, G. Refael, and F. von Oppen, Helical Liquids and Majorana Bound States in Quantum Wires, Phys. Rev. Lett. 105, 177002 (2010).

- [19] A. Das, Y. Ronen, Y. Most, Y. Oreg, M. Heiblum, and H. Shtrikman, Zero-bias peaks and splitting in an Al-InAs nanowire topological superconductor as a signature of Majorana fermions, Nat. Phys. 8, 887 (2012).

- [20] S. M. Albrecht, A. P. Higginbotham, M. Madsen, F. Kuemmeth, T. S. Jespersen, J. Nygård, P. Krogstrup, and C. M. Marcus, Exponential protection of zero modes in Majorana islands, Nature (London) 531, 206 (2016).

- [21] A. P. Higginbotham, S. M. Albrecht, G. Kirsanškas, W. Chang, F. Kuemmeth, P. Krogstrup, T. S. Jespersen, J. Nygård, K. Flensberg, and C. M. Marcus, Parity lifetime of bound states in a proximitized semiconductor nanowire, Nat. Phys. 11, 1017 (2015).

- [22] T. A. Fulton and G. J. Dolan, Observation of Single-Electron Charging Effects in Small Tunnel Junctions, Phys. Rev. Lett. 59, 109 (1987).

- [23] H. Grabert and M. H. Devoret, *Single Charge Tunneling* (Plenum, New York, 1992).

- [24] D. V. Averin and J. P. Pekola, Nonadiabatic Charge Pumping in a Hybrid Single-Electron Transistor, Phys. Rev. Lett. **101**, 066801 (2008).

- [25] V. F. Maisi, O.-P. Saira, Yu. A. Pashkin, J. S. Tsai, D. V. Averin, and J. P. Pekola, Real-Time Observation of Discrete Andreev Tunneling Events, Phys. Rev. Lett. 106, 217003 (2011).

- [26] Z. Zhong, Y. Fang, W. Lu, and C. M. Lieber, Coherent single charge transport in molecular-scale silicon nanowires, Nano Lett. 5, 1143 (2005).

- [27] M. Hofheinz, X. Jehl, M. Sanquer, G. Molas, M. Vinet, and S. Deleonibus, Simple and controlled single electron transistor based on doping modulation in silicon nanowires, Appl. Phys. Lett. 89, 143504 (2006).

- [28] C. Thelander, T. Mårtensson, M. T. Björk, B. J. Ohlsson, M. W. Larsson, L. R. Wallenberg, and L. Samuelson, Single-electron transistors in heterostructure nanowires, Appl. Phys. Lett. 83, 2052 (2003).

- [29] R. Popovitz-Biro, A. Kretinin, P. Von Huth, and H. Shtrikman, InAs/GaAs core-shell nanowires, Cryst. Growth Des. 11, 3858 (2011).

- [30] J. W. W. van Tilburg, R. E. Algra, W. G. G. Immink, M. Verheijen, E. P. A. M. Bakkers, and L. P. Kouwenhoven, Surface passivated InAs/InP core/shell nanowires, Semicond. Sci. Technol. 25, 024011 (2010).

- [31] A. C. E. Chia, M. Tirado, Y. Li, S. Zhao, Z. Mi, D. Comedi, and R. R. LaPierre, Electrical transport and optical model of GaAs-AlInP core-shell nanowires, J. Appl. Phys. 111, 094319 (2012).

- [32] A. Lin, J. N. Shapiro, A. C. Scofield, B. L. Liang, and D. L. Huffaker, Enhanced InAs nanopillar electrical transport by *in-situ* passivation, Appl. Phys. Lett. **102**, 053115 (2013).

- [33] G. W. Holloway, Y. Song, C. M. Haapamaki, R. R. LaPierre, and J. Baugh, Electron transport in InAs-InAlAs core-shell nanowires, Appl. Phys. Lett. 102, 043115 (2013).

- [34] B. Ganjipour, S. Sepehri, A. W. Dey, O. Tizno, B. M. Borg, K. A. Dick, L. Samuelson, L.-E. Wernersson, and C. Thelander, Electrical properties of GaSb/InAsSb core/shell nanowires, Nanotechnology 25, 425201 (2014).

- [35] K. Gloos, P. J. Koppinen, and J. P. Pekola, Properties of native ultrathin aluminium oxide tunnel barriers, J. Phys. Condens. Matter 15, 1733 (2003).

- [36] O. Wunnicke, Gate capacitance of back-gated nanowire field-effect transistors, Appl. Phys. Lett. 89, 083102 (2006).

- [37] A. C. Bleszynski, F. A. Zwanenburg, R. M. Westervelt, A. L. Roest, E. P. A. M. Bakkers, and L. P. Kouwenhoven, Scanned probe imaging of quantum dots inside InAs nanowires, Nano Lett. 7, 2559 (2007).

- [38] E. E. Boyd, K. Storm, L. Samuelson, and R. M. Westervelt, Scanning gate imaging of quantum dots in 1*d* ultra-thin InAs/InP nanowires, Nanotechnology **22**, 185201 (2011).

- [39] M. D. Schroer and J. R. Petta, Correlating the nanostructure and electronic properties of InAs nanowires, Nano Lett. 10, 1618 (2010).

- [40] K. Weis, S. Wirths, A. Winden, K. Sladek, H. Hardtdegen, H. Lüth, D. Grützmacher, and T. Schäpers, Quantum dots in InAs nanowires induced by surface potential fluctuations, Nanotechnology 25, 135203 (2014).

- [41] J. P. Pekola, J. J. Vartiainen, M. Möttönen, O.-P. Saira, M. Meschke, and D. V. Averin, Hybrid single-electron transistor as a source of quantized electric current, Nat. Phys. 4, 120 (2008).

- [42] Y.-J. Doh, S. De Franceschi, E. P. A. M. Bakkers, and L. P. Kouwenhoven, Andreev reflection versus Coulomb blockade in hybrid semiconductor nanowire devices, Nano Lett. 8, 4098 (2008).

- [43] R. C. Dynes, V. Narayanamurti, and J. P. Garno, Direct Measurement of Quasiparticle-Lifetime Broadening in a Strong-Coupled Superconductor, Phys. Rev. Lett. 41, 1509 (1978).

- [44] R. C. Dynes, J. P. Garno, G. B. Hertel, and T. P. Orlando, Tunneling Study of Superconductivity near the Metal-Insulator Transition, Phys. Rev. Lett. 53, 2437 (1984).