# Experimental Demonstration of XOR Operation in Graphene Magnetologic Gates at Room Temperature

Hua Wen,<sup>1,2</sup> Hanan Dery,<sup>3,\*</sup> Walid Amamou,<sup>1</sup> Tiancong Zhu,<sup>2</sup> Zhisheng Lin,<sup>1</sup> Jing Shi,<sup>1</sup> Igor Žutić,<sup>4</sup> Ilya Krivorotov,<sup>5</sup> L. J. Sham,<sup>6,†</sup> and Roland K. Kawakami<sup>1,2,‡</sup>

<sup>1</sup>Department of Physics and Astronomy, University of California, Riverside, Riverside, California 92521, USA

<sup>2</sup>Department of Physics, The Ohio State University, Columbus, Ohio 43210, USA <sup>3</sup>Department of Electrical and Computer Engineering, University of Rochester,

Rochester, New York 14627, USA

<sup>4</sup>Department of Physics, University at Buffalo, State University of New York,

Buffalo, New York 14260, USA

<sup>5</sup>Department of Physics and Astronomy, University of California, Irvine, Irvine, California 92697, USA <sup>6</sup>Department of Physics, University of California, San Diego, La Jolla, California 92697, USA (Received 29 November 2015; revised manuscript received 12 February 2016; published 4 April 2016)

We report the experimental demonstration of a magnetologic gate built on graphene at room temperature. This magnetologic gate consists of three ferromagnetic electrodes contacting a single-layer graphene spin channel and relies on spin injection and spin transport in the graphene. We utilize electrical bias tuning of spin injection to balance the inputs and achieve "exclusive or" (XOR) logic operation. Furthermore, a simulation of the device performance shows that substantial improvement towards spintronic applications can be achieved by optimizing the device parameters such as the device dimensions. This advance holds promise as a basic building block for spin-based information processing.

# DOI: 10.1103/PhysRevApplied.5.044003

### I. INTRODUCTION

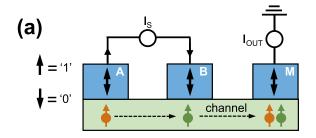

Spintronics is an approach to electronics that utilizes the spin of the electron for information storage and processing [1–3]. By providing the ability to integrate logic with nonvolatile storage in ferromagnetic data registers, spintronics could greatly reduce the power consumption in logic circuits and go beyond traditional CMOS architectures. The demonstration of spin injection into semiconductors [4,5] prompted a variety of proposals for spintronic devices, taking advantage of the tunable nature of semiconductors [6–11]. Among these was a proposal by Dery and Sham [12] for an "exclusive or" (XOR) gate based on spin accumulation in a semiconductor channel contacted by three ferromagnetic (FM) electrodes [see Fig. 1(a)]. In this device, the magnetization directions of the first two FM electrodes represent the logic inputs (0 and 1), and spin injection from these input electrodes generates a current through the third FM electrode which represents the logic output. Subsequently, a more general proposal was developed that combines two such XOR gates to form a universal reconfigurable magnetologic gate (MLG) [8]. This MLG consists of five FM electrodes and the logic operation is represented by OR[XOR(A, B), XOR(C, D)], where A, B, C and D are the four logical input states and the fifth FM electrode reads the output. This can also be utilized as a universal two-input gate, where *B* and *D* define the gate operation (e.g., NAND, OR) and *A* and *C* represent the two inputs. The experimental discoveries of room-temperature spin transport [13] and efficient spin injection into graphene [14] provided an ideal materials platform to realize such MLG devices. Motivated by these advances, the theoretical performance of graphene-based MLG was analyzed and novel spintronic circuits for rapid parallel searching were developed [15]. However, despite these extensive advances in the device modeling and spintronic circuit design, the experimental demonstration of the proposed three-terminal XOR and five-terminal universal MLG has been lacking.

In this article, we experimentally demonstrate the proposed three-terminal XOR magnetologic-gate operation in a graphene spintronic device at room temperature. By carefully tuning the bias current between the two input electrodes, and an offset voltage in the detection loop, a clear nonzero output current (logic 1) is observed when the two inputs are antiparallel, with an absolute zero output current (logic 0) when the two inputs are parallel. These results provide the proof-of-concept demonstration for a class of magnetologic devices based on spin accumulation and establish the feasibility of the universal five-terminal MLG. While our advances are based on individual properties observed previously, the novelty comes from integrating these individual components in an unconventional way

hdery@ur.rochester.edu

lsham@ucsd.edu

<sup>‡</sup>kawakami.15@osu.edu

FIG. 1. Experimental demonstration of graphene XOR magnetologic gate. (a) Diagram of proposed XOR magnetologic-gate device. A, B, and M are ferromagnetic electrodes on top of a spin-transport channel. Input logic 1 and 0 are the two magnetization directions along the easy axis of the electrodes.  $I_S$  injects spins through the two inputs, A and B.  $I_{out}$  is the logic output signal. (b) Illustration of experimental device structure and measurement setup. A, B, and M are MgO/Co electrodes. The spin channel is a single-layer graphene. R is Ti/Au nonmagnetic reference electrode used as ground point.  $I_{\rm out}$  and  $V_{\rm out}$  are the measured current and voltage signal, respectively.  $R_{\rm sen}$  is a variable resistor.  $V_{\rm offs}$  is an ac voltage source. External magnetic field H is applied to the easy axis of the electrodes. Center-to-center distances of the electrodes are  $L_{AB}=1.6~\mu\mathrm{m}, L_{\mathrm{BM}}=1.8~\mu\mathrm{m}.~L_{\mathrm{MR}}=7.85~\mu\mathrm{m}.$  Graphene width along the H direction is  $\sim$ 4.3  $\mu$ m. (c)  $I_{out}$  measured as a function of H. Black (red) curve indicates H sweeps upwards (downwards). Vertical arrows indicate the magnetization states of A and B. Top left inset: truth table of XOR logic operation.

to achieve the desired logic function. Moreover, instead of using nonlocal lateral spin valves merely as a vehicle to demonstrate spin injection, our results show a tangible way to make use of the injected spin accumulation in similar devices for logic purposes. Furthermore, the signal size of the logic 1 output can be significantly enhanced by reducing the device size according to numerical simulation, making it promising for future spintronic applications.

## II. EXPERIMENTAL SETUP AND RESULTS

The device geometry and measurement circuit are shown in Fig. 1(b). A flake of mechanically exfoliated single-layer graphene is contacted by ferromagnetic cobalt (Co) electrodes A, B, and M through MgO tunnel barriers [14,16]. The source current  $I_S$  is a combination of  $I_{ac}$  (ac current to inject spins) and  $I_{\rm dc}$  (dc bias current). The output voltage  $V_{\rm out}$  (ac voltage) is measured using standard low-frequency lock-in techniques, and output current  $I_{\text{out}}(=V_{\text{out}}/R_{\text{sen}})$  is determined using a current detection scheme by systematically tuning the variable sensing resistor  $R_{\text{sen}}$  [17]. An offset voltage  $V_{\rm offs}$  (ac voltage with phase and frequency locked to  $I_{ac}$ ) is used to eliminate any background signal unrelated to spin. Reference electrode R (Ti/Au) is fabricated at the end of graphene and used as the ground point. Back-gate voltage  $V_G$  is applied on the Si substrate to tune the graphene carrier density.

Figure 1(c) shows the experimental demonstration of the XOR logic operation for a representative device. The four different input states are realized by sweeping an external magnetic field (H, collinear with the easy axes of the ferromagnets) to individually switch the magnetizations of input electrodes A and B, which have different magneticshape anisotropy. The magnetization of M is kept downward during the logic operation. The measured  $I_{\text{out}}$  varies with the different input states and demonstrates the XOR logic operation. When the inputs are parallel (00 or 11),  $|I_{\text{out}}|$  is less than 0.023 nA. When the inputs are antiparallel (01 or 10),  $|I_{\text{out}}|$  is stable at about 0.11 nA. The truth table of this XOR gate is summarized in the inset of Fig. 1(c). In the rest of the paper, we explain how this XOR logic operation is achieved and how the output signal could be optimized for future applications.

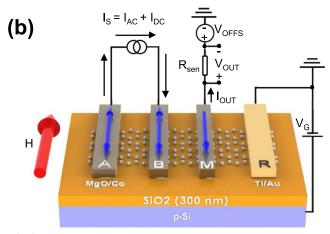

An important preliminary step is the validation of the spin-transport properties using traditional nonlocal voltage detection [13,18]. For the measurement circuit in Fig. 1(b), bias current  $I_{\rm dc}$  and offset voltage  $V_{\rm offs}$  are set to zero and  $R_{\rm sen}$  is adjusted to be sufficiently large (10 M $\Omega$ ) to perform voltage detection [17]. For the device under investigation, the Dirac point is located at  $V_G = -13$  V [19], and  $V_G$  is set to +30 V for the measurements. Electron spins are injected through inputs A and B using a current of  $I_{\rm ac} = 1~\mu{\rm A}$  (11 Hz). Figure 2(a) shows the nonlocal voltage  $V_{\rm out}$  at different magnetization states of A, B, and M. We observe three jumps in  $V_{\rm out}$  as the magnetic field H is swept upward or downward, which correspond to the

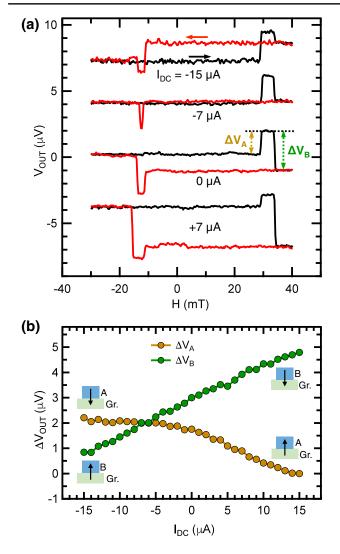

FIG. 2. Nonlocal voltage detection of spin transport. (a) and (b) Voltage signal  $V_{\rm out}$  as a function of H for a full sweep [(a) -45 mT to +60 mT] and minor loop [(b) -20 mT to +40 mT].  $I_S = I_{\rm ac} = 1~\mu A$ . In (b), only A and B switch their magnetization. The change of  $V_{\rm out}$  when A (B) switches its magnetization direction is noted as  $\Delta V_A$  ( $\Delta V_B$ ). M is fixed to be  $\downarrow$ .

magnetization switching of the three ferromagnets. This indicates successful spin injection, transport, and detection in our device [20].

In order to examine the logic operation of our device, the output electrode needs to be maintained at fixed magnetization. This is possible because electrode M has a distinct, and, more importantly, larger coercive field than A and B. It is worth noting that the coercive field of the electrodes are different for positive and negative fields due to the geometrical shape of the electrodes, which can create domain-wall pinning [16,21]. However, it is found that the magnetic field required to switch M from  $\downarrow$  to  $\uparrow$  is significantly larger than that of A and B, as shown in Fig. 2(a). Therefore, M is initially magnetized to be  $\downarrow$  and then H is swept below +44 mT. In this way, the magnetization state of M is fixed at  $\downarrow$  throughout the logic operation.

Figure 2(b) shows the voltage signal  $V_{\text{out}}$  with four different input states  $(\downarrow\downarrow,\uparrow\downarrow,\uparrow\uparrow,\uparrow\uparrow,$  and  $\downarrow\uparrow)$  when H is swept between -20 mT and +40 mT. The input states are realized in the following order:  $\downarrow\downarrow,\uparrow\downarrow,\uparrow\downarrow,\uparrow\uparrow,\downarrow\downarrow$ , when H is swept through -20 mT  $\rightarrow +40$  mT  $\rightarrow -20$  mT. We observe that for antiparallel inputs,  $V_{\text{out}}$  has different values compared to parallel inputs. However, two challenges need to be overcome in order for  $V_{\text{out}}$  to produce the proper logic output signal. The first challenge is that input A contributes a smaller signal to the output compared to input B due to the fact that input A is further away from A than input A. This is indicated by the different values of  $\Delta V_A$  and  $\Delta V_B$  in

Fig. 2(b). The second challenge is that  $V_{\rm out}$  is not zero for parallel inputs. These two problems make it difficult to discriminate between logic 0 and 1. In the following, we present our methods to resolve these challenges.

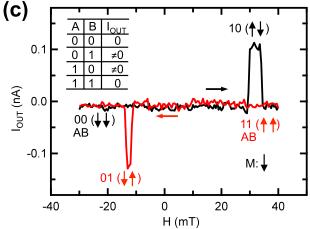

To tune the signal contribution of inputs A and B, a dc bias current  $I_{dc}$  is added in the injection current loop as shown in Fig. 1(b), where positive  $I_{dc}$  is defined as current flowing from B, through the graphene, to A. It was previously shown that the nonlocal spin signal can be significantly tuned by a dc bias current [22,23]. Similar bias dependence is observed in our devices, with the spin signal increasing at positive bias (current flowing from electrode to graphene) and decreasing at negative bias [19]. Because inputs A and B are under opposite bias when  $I_{dc}$  flows through the injection circuit, we can tune the spin signal from input A ( $\Delta V_A$ ) and input B ( $\Delta V_B$ ) in an opposite manner. This is illustrated in Figs. 3(a) and 3(b), where  $I_{\rm dc}$ is varied from  $-15 \mu A$  to  $+15 \mu A$ . As  $I_{dc}$  is increased, the value of  $\Delta V_A$  decreases while the value of  $\Delta V_B$  increases. Notably, when  $I_{dc}$  is at  $-7 \mu A$ , the spin signals from inputs A and B are equal  $(\Delta V_A = \Delta V_B)$ . This results in the balanced output curve as shown in Fig. 3(a) for  $I_{\rm dc} = -7 \ \mu A$ . We have reproduced this tuning and balancing of the two inputs on multiple devices with MgO and Al<sub>2</sub>O<sub>3</sub> tunnel barriers [19].

To tune the logic 0 output to actual zero,  $V_{\rm offs}$  is added in the detection loop [Fig. 1(b)]. The output 0 level (defined as the background signal  $V_{\rm bg}$ ) is systematically adjusted by varying  $V_{\rm offs}$  [19]. For the device presented in this paper,  $V_{\rm bg}$  is close to zero when  $V_{\rm offs}=+8~\mu{\rm V}$ .

In order to utilize this spin-based MLG in the proposed spintronic circuit [8,15], we need to convert the logic output from a voltage signal to a current signal. The current output allows the integration of multiple XOR MLGs before doing spin-to-charge conversion. This can greatly reduce the power consumption when performing large data search applications by using this XOR gate as compared to traditional CMOS devices [15]. By utilizing the current detection scheme developed for graphene spin valves [17], we achieve a current output for our XOR logic with sufficiently small  $R_{\rm sen}$  (1–3 k $\Omega$ , see Ref. [19]). The resulting current output signal is shown in Fig. 1(c), with  $R_{\text{sen}} = 3 \text{ k}\Omega$ ,  $I_{\rm dc} = -7 \ \mu \text{A}$ , and  $V_{\rm offs} = +8 \ \mu \text{V}$ . This curve displays precisely the behavior needed for the XOR magnetologic gate [12]. When the two inputs are 00 or 11, the output current is zero (logical 0), and when the two inputs are 01 or 10, the output current is nonzero (logical 1). We note that the output currents of 01 and 10 logic states have opposite polarities. On one hand, this can be rectified in circuits where the opposite polarity is undesirable. On the other hand, when this XOR gate is considered as a building block for the more complex five-terminal MLG, the opposite polarity of the output is essential [8,15].

While this proof-of-concept demonstration of a graphene-based magnetologic gate shows promise for

FIG. 3. Tuning  $\Delta V_A$  and  $\Delta V_B$  using bias current  $I_{\rm dc}$ . (a)  $V_{\rm out}$  as a function of H [minor loop, as in Fig. 2(b)] at different  $I_{\rm dc}$ . Curves are shifted vertically for clarity. (b)  $\Delta V_A$  and  $\Delta V_B$  as a function of  $I_{\rm dc}$ . At positive (negative)  $I_{\rm dc}$ , B is under positive (negative) bias and A is under negative (positive) bias. Vertical arrows indicate the flow of current  $I_{\rm dc}$ . "Gr." represents the graphene channel.

future spintronics devices, several key improvements are needed for practical applications of the gate. First, writing of the magnetic information should be facilitated by spintransfer torque (STT) techniques [24] or spin Hall effect [25,26] (SHE) that alleviates the need for external magnetic fields and different shapes for contacts. We note that STT and SHE can be achieved by an all-metallic path, with no current leakage to graphene [14]. Second, the operation should be independent of device-specific bias current ( $I_{\rm dc}$ ) and offset voltage ( $V_{\rm offs}$ ). For the former, this can be achieved by engineering device parameters including spin polarization of the contacts, geometric size of contacts and graphene, the spin diffusion length of graphene, etc., and is

further discussed in the following paragraphs. For the latter,  $V_{\rm offs}$  is used to cancel the *spin-independent* signal that is present in many nonlocal spin-valve measurements, but whose origin is unknown. Further studies on the origin of this background would be extremely helpful in this regard [27]. However, in spintronic circuits of the type proposed by Dery and Sham [8,15], the oscillating magnetization of the readout electrode (M) will extract only the *spin-dependent* part of the signal, thereby alleviating the need for  $V_{\rm offs}$ .

# III. SIMULATION ON OPTIMIZED DEVICES AND DISCUSSION

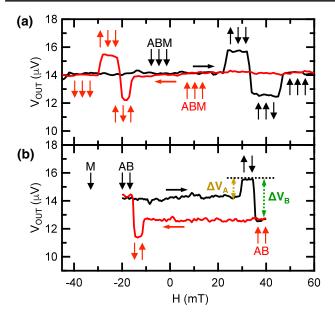

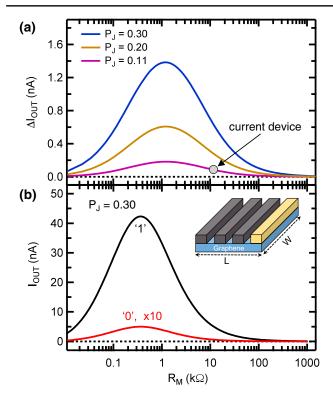

We simulate the output current signal for various critical device parameters using a one-dimensional spin drift-diffusion model considering finite-size contacts [19,28]. The current spin polarization of electrode A, B, and M are assumed to be of the same  $(P_I)$ .  $P_I$  is experimentally measured to be ~0.11 in the presented device. Figure 4(a) shows the signal difference ( $\Delta I_{\text{out}}$ ) between 1 and 0 output  $(\Delta I_{\rm out} = |I_{\rm out}(1) - I_{\rm out}(0)|)$  for  $P_J = 0.11,~0.20,~0.30.$  Increasing  $P_J$  is found to significantly increase  $\Delta I_{\text{out}}$ .  $\Delta I_{\text{out}}$  can be enhanced even further with higher  $P_J$  using alternative tunnel barriers [29]. Interestingly, we find that contact resistance of  $M(R_M)$ plays an important role in optimizing the output current.  $I_{\rm out}$  exhibits a maximum at  $R_M \sim 1.2~{\rm k}\Omega$ . This optimal  $R_M$ depends on the graphene size and the spin diffusion length of graphene (2.2  $\mu$ m in the present device as determined through Hanle precession [20]). For lower  $R_M$ , contactinduced spin relaxation reduces the spin accumulation and thus reduces the output current [30]. For higher  $R_M$ , the increased resistance of the detection circuit reduces the output current [17]. The current at optimal  $R_M$  is about 2 times larger than the output current for  $R_M \sim 11.5 \text{ k}\Omega$  in the presented device [gray dot in Fig. 4(a)].

The performance of the device can be further improved by working in a confined geometry. Figure 4(b) shows the simulated current for logic 0 and 1 output for a much smaller device (shown in the inset). This device has a size of 350 nm  $\times$  500 nm ( $L \times W$ ) and there is no graphene extending outside of electrodes A and R [19]. The current for 1 output is 2 orders of magnitude larger than 0 output due to the reduced spacing (center-to-center distance is 100 nm) between the two inputs, A and B. In such a confined device, the logic operation is simplified since there is no need for adding  $I_{dc}$  to balance the contribution of inputs A and B because the electrode spacing is much less than the spin diffusion length [31]. This simplification is crucial for large-scale integration of these devices into logic circuits. Whereas scaling down the feature size in modern CMOS technology leads to undesirable leakage currents, the performance of our MLGs will continue to improve with further reduction of the distance between contacts [15].

FIG. 4. Optimizing output current signal. (a) Signal difference between 1 and 0 logic output  $\Delta I_{\rm out}$  ( $\equiv |I_{\rm out}(1)-I_{\rm out}(0)|$ ) as a function of  $R_M$  for different spin polarization of contacts, assuming  $P_A=P_B=P_M=P_J$ , and  $P_R=0$ . The gray dot represents our current device parameters. (b) Output signal  $I_{\rm out}$  (1 and 0) as a function of  $R_M$  for an optimized device geometry. The signal for 0 is magnified by 10 times. Inset: optimized device structure. There is no graphene beyond electrodes A and B. The whole device length is L=350 nm. The graphene width is B=500 nm. Each electrode (A, B, B, and B) has a width of B0 nm, and the center-to-center distance between adjacent electrodes is 100 nm. Spin polarization  $B_J$ 1 is 0.30.

Finally, we discuss two issues related to the practical implementation of the MLG into circuits, namely, cascading and operation speed. For general purpose logic, one method for cascading MLGs is to use the small output current  $I_{\text{out}}$  as a trigger for a thyristor latch, which will drive larger currents for writing the magnetizations of subsequent MLG input electrodes [8]. Alternatively, one could use a current amplifier on  $I_{\text{out}}$  to switch the input of a subsequent MLG by spin torque. Meanwhile, for certain types of logic applications such as search engines, specially designed circuits require only one CMOS amplifier to be used for every ~100 MLGs [15]. Through such design, the overall circuit can be much more efficient due to the minimum interface with CMOS. For the issue of operation speed, some important considerations are the switching time for the FM electrode, the RC time constant of the contact, and the spin-transport time across the graphene channel. As discussed in Ref. [15], the switching times are on the order of  $\sim$ 1 ns and the RC time constant is on the order of  $\sim$ 80 ps (for 200 k $\Omega$  resistance and 0.4 fF parallel capacitance). The spin-transport time across 1  $\mu$ m of high mobility graphene is  $\sim$ 12 ps (diffusion constant of 0.08 m<sup>2</sup>/s, as in Ref. [32]). While all these factors can be substantially improved, the most important limiting factor at present is the switching time of the FM electrode.

### IV. CONCLUSION

In conclusion, we have demonstrated a graphene MLG that performs XOR logic at room temperature. The key step is to systematically tune the injection current bias to balance the contributions of the two input ferromagnetic electrodes to the output signal. With further reduction of the graphene area and optimization of the magnetic contacts (resistance and spin polarization), these MLGs will improve the performance of information-processing integrated circuits.

### ACKNOWLEDGMENTS

The authors acknowledge Y. Kato and B. Bushong for helpful discussions. This work was supported by NRI-NSF (DMR-1124601). We also acknowledge the support from ONR (N00014-14-1-0350), NSF (DMR-1310661), NSF-MRSEC (DMR-1420451), NSF (ECCS-1231570), NSF (ECCS-1508873), NSF (ECCS-1309416), DTRA (HDTRA1-13-1-0013), ONR (N00014-13-1-0754), and C-SPIN, one of the six SRC STARnet Centers, sponsored by MARCO and DARPA.

- [1] S. A. Wolf, D. D. Awschalom, R. A. Buhrman, J. M. Daughton, S. von Molnar, M. L. Roukes, A. Y. Chtchelkanova, and D. M. Treger, Spintronics: A spin-based electronics vision for the future, Science 294, 1488 (2001).

- [2] I. Žutić, J. Fabian, and D. Das Sarma, Spintronics: Fundamentals and applications, Rev. Mod. Phys. 76, 323 (2004).

- [3] S. Maekawa, Concepts in Spin Electronics (Oxford, New York, 2006).

- [4] Y. Ohno, D. K. Young, B. Beschoten, F. Matsukura, H. Ohno, and D. D. Awschalom, Electrical spin injection in a ferromagnetic semiconductor heterostructure, Nature (London) 402, 790 (1999).

- [5] R. Fiederling, M. Keim, G. Reuscher, W. Ossau, G. Schmidt, A. Waag, and L. W. Molenkamp, Injection and detection of a spin-polarized current in a light-emitting diode, Nature (London) 402, 787 (1999).

- [6] M. E. Flatté, Z. G. Yu, E. Johnston-Halperin, and D. D. Awschalom, Theory of semiconductor magnetic bipolar transistors, Appl. Phys. Lett. 82, 4740 (2003).

- [7] S. Sugahara and M. Tanaka, A spin metal-oxidesemiconductor field-effect transistor using half-metallicferromagnet contacts for the source and drain, Appl. Phys. Lett. 84, 2307 (2004).

- [8] H. Dery, P. Dalal, L. Cywinski, and L. J. Sham, Spin-based logic in semiconductors for reconfigurable large-scale circuits, Nature (London) 447, 573 (2007).

- [9] J. Fabian and I. Žutić, Spin-polarized current amplification and spin injection in magnetic bipolar transistors, Phys. Rev. B 69, 115314 (2004).

- [10] E. Johnston-Halperin, D. Lofgreen, R. K. Kawakami, D. K. Young, L. Coldren, A. C. Gossard, and D. D. Awschalom, Spin-polarized Zener tunneling in (Ga,Mn)As, Phys. Rev. B 65, 041306 (2002).

- [11] I. Žutić, J. Fabian, and S. Das Sarma, Spin-Polarized Transport in Inhomogeneous Magnetic Semiconductors: Theory of Magnetic/Nonmagnetic *p-n* Junctions, Phys. Rev. Lett. **88**, 066603 (2002).

- [12] H. Dery, Ł. Cywiński, and L. J. Sham, Spin transference and magnetoresistance amplification in a transistor, Phys. Rev. B 73, 161307 (2006).

- [13] N. Tombros, C. Jozsa, M. Popinciuc, H. T. Jonkman, and B. J. van Wees, Electronic spin transport and spin precession in single graphene layers at room temperature, Nature (London) 448, 571 (2007).

- [14] W. Han, K. Pi, K. M. McCreary, Y. Li, J. J. I. Wong, A. G. Swartz, and R. K. Kawakami, Tunneling Spin Injection into Single Layer Graphene, Phys. Rev. Lett. 105, 167202 (2010).

- [15] H. Dery, W. Hui, B. Ciftcioglu, M. Huang, S. Yang, R. Kawakami, S. Jing, I. Krivorotov, I. Žutić, and L. J. Sham, Nanospintronics based on magnetologic gates, IEEE Trans. Electron Devices 59, 259 (2012).

- [16] W. Han, K. M. McCreary, K. Pi, W. H. Wang, Y. Li, H. Wen, J. R. Chen, and R. K. Kawakami, Spin transport and relaxation in graphene, J. Magn. Magn. Mater. 324, 369 (2012).

- [17] H. Wen, T. Zhu, Y. Luo, W. Amamou, and R. K. Kawakami, Current-based detection of nonlocal spin transport in graphene for spin-based logic applications, J. Appl. Phys. 115, 17B741 (2014).

- [18] M. Johnson and R. H. Silsbee, Interfacial Charge-Spin Coupling: Injection and Detection of Spin Magnetization in Metals, Phys. Rev. Lett. 55, 1790 (1985).

- [19] See Supplemental Material at http://link.aps.org/supplemental/10.1103/PhysRevApplied.5.044003 for more details on device characteristics, XOR operation using  $Al_2O_3$  tunnel barrier, output signal tuning using  $V_{\rm offs}$ ,  $I_{\rm out}$  for different  $R_{\rm sen}$ , and simulation of  $I_{\rm out}$ .

- [20] W. Han, R. K. Kawakami, M. Gmitra, and J. Fabian, Graphene spintronics, Nat. Nanotechnol. 9, 794 (2014).

- [21] A. J. Berger, M. R. Page, H. Wen, K. M. McCreary, V. P. Bhallamudi, R. K. Kawakami, and P. Chris, Hammel, Correlating spin transport and electrode magnetization in a graphene spin valve: Simultaneous magnetic microscopy and non-local measurements, Appl. Phys. Lett. 107, 142406 (2015).

- [22] C. Jozsa, M. Popinciuc, N. Tombros, H. T. Jonkman, and B. J. van Wees, Controlling the efficiency of spin injection into graphene by carrier drift, Phys. Rev. B 79, 081402 (2009).

- [23] W. Han, W. H. Wang, K. Pi, K. M. McCreary, W. Bao, Y. Li, F. Miao, C. N. Lau, and R. K. Kawakami, Electron-Hole Asymmetry of Spin Injection and Transport in Single-Layer Graphene, Phys. Rev. Lett. 102, 137205 (2009).

- [24] D. C. Ralph and M. D. Stiles, Spin transfer torques, J. Magn. Magn. Mater. 320, 1190 (2008).

- [25] L. Liu, C.-F. Pai, Y. Li, H. W. Tseng, D. C. Ralph, and R. A. Buhrman, Spin-torque switching with the giant spin Hall effect of tantalum, Science 336, 555 (2012).

- [26] K. Garello, C. O. Avci, I. M. Miron, M. Baumgartner, A. Ghosh, S. Auffret, O. Boulle, G. Gaudin, and P. Gambardella, Ultrafast magnetization switching by spinorbit torques, Appl. Phys. Lett. 105, 212402 (2014).

- [27] S. Garzon, I. Zutic, and R. A. Webb, Temperature Dependent Asymmetry of the Nonlocal Spin-Injection Resistance: Evidence for Spin Non-Conserving Interface Scattering, Phys. Rev. Lett. 94, 176601 (2005).

- [28] H. Dery, L. Cywinski, and L. J. Sham, Lateral diffusive spin transport in layered structures, Phys. Rev. B 73, 041306 (2006).

- [29] A. L. Friedman, O. M. J. van 't Erve, C. H. Li, J. T. Robinson, and B. T. Jonker, Homoepitaxial tunnel barriers with functionalized graphene-on-graphene for charge and spin transport, Nat. Commun. 5, 3161 (2014).

- [30] W. Han, K. Pi, W. Bao, K. M. McCreary, Y. Li, W. H. Wang, C. N. Lau, and R. K. Kawakami, Electrical detection of spin precession in single-layer graphene spin valves with transparent contacts, Appl. Phys. Lett. 94, 222109 (2009).

- [31] M. H. D. Guimarães, J. J. van den Berg, I. J. Vera-Marun, P. J. Zomer, and B. J. van Wees, Spin transport in graphene nanostructures, Phys. Rev. B 90, 235428 (2014).

- [32] M. H. D. Guimarães, P. J. Zomer, J. Ingla-Aynés, J. C. Brant, N. Tombros, and B. J. van Wees, Controlling Spin Relaxation in Hexagonal BN-Encapsulated Graphene with a Transverse Electric Field, Phys. Rev. Lett. 113, 086602 (2014).